### User's Guide

# REF70EVM User's Guide

### **ABSTRACT**

The REF70EVM is a precision voltage reference evaluation module that demonstrates the REF70 ultra-low noise integrated circuit from Texas Instruments (TI).

### **Table of Contents**

| Irademarks                                  | 1              |

|---------------------------------------------|----------------|

| 1 Overview                                  | 2              |

| 1.1 REF70EVM Features                       | 2              |

| 1.2 REF70EVM Schematic                      | 3              |

| 1.3 REF70EVM Bill of Materials              | 4              |

| 1.3 REF70EVM Bill of Materials              | 5              |

| 2 Quick Setup Guide                         | 6              |

| 2.1 Electrostatic Discharge Warning         | 6              |

| 2.2 Unpacking the EVM                       |                |

| 2.3 Power Supply Setup and Functional Test. | 6              |

| 3 EVM Theory and Operation                  | <mark>7</mark> |

| 3.1 V <sub>REF</sub> Output's OUTF and OUFS | 7              |

| 3.2 Output Capacitor                        | <mark>7</mark> |

| 4 Layout and Component Placement            |                |

#### **Trademarks**

All other trademarks are the property of their respective owners.

Overview www.ti.com

#### 1 Overview

The REF70EVM is an adjustable voltage reference evaluation module that demonstrates the REF70 integrated circuit in its FKH ceramic package from Texas Instruments (TI).

The REF70 is a ultra-low noise voltage reference with 2 ppm/C temperature drift. The REF70 is used primarily as a voltage reference for high accuracy data converters to allow for a larger noise free resolution.

The REF70 can be operated from  $V_{REF}$  to 18 V, making this part optimal for a wide range of voltages for applications such as precision data acquasition systems, industrial instrumentation, semiconductor test equipment, and PLC analog I/O modules. In order for this device to operate as intended, it does require 6.5 mA  $I_Q(max)$  for proper operating across temperature. This device also comes with a enable pin that allows the device to be set in shutdown mode. Under the shutdown condition, the REF70 only consumes 12  $\mu$ A of current.

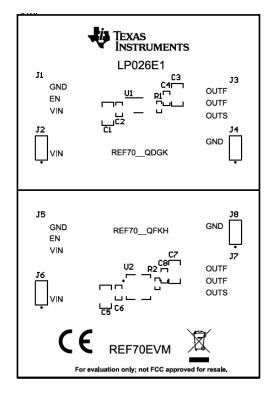

The REF70EVM is configured for a LCCC (FKH) ceramic package (U2) and includes a additional MSSOP (DGK) landpattern for alternate packages (U1). The VIN header can be connected to an external power supply to provide power. All of the REF70 input and output pins are accessible for external connection via test headers. For users looking for a alternate packages to test the REF70, contact TI.

#### 1.1 REF70EVM Features

- Includes: REF7025QFKH

- · Footprints for resistors and capacitors

- · Multiple outputs for voltage measurements

| KEY PARAMETERS        | PARAMETER | PARAMETER LIMITS |  |

|-----------------------|-----------|------------------|--|

| Supply Voltage:       | IN        | 0 V – 18V        |  |

| Enable Pin            | EN        | 0V to IN         |  |

| Fixed Output Voltage: | VREF      | 2.5 V (REF7025)  |  |

| Output Current:       | IOUT      | -10 mA to 10 mA  |  |

#### **CAUTION**

Applying voltages above the limitations given in this table may cause permanent damage to your hardware.

www.ti.com Overview

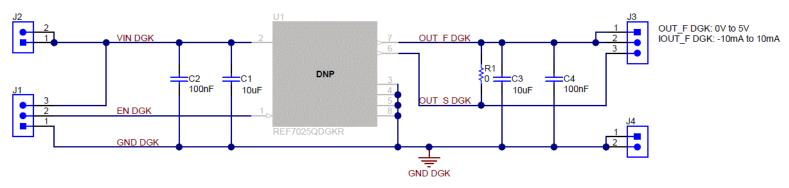

#### 1.2 REF70EVM Schematic

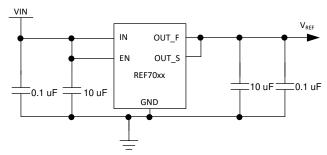

The schematic for the REF70EVM is illustrated in Figure 1-1.

VIN DGK: 0V to 18V EN DGK: 0V to 18V IDD: 0mA to 17mA

VIN FKH: 0V to 18V EN FKH: 0V to 18V IDD: 0mA to 17mA

Figure 1-1. REF70EVM Schematic

Overview www.ti.com

## 1.3 REF70EVM Bill of Materials

| DESIGNATOR                     | QUANTITY | VALUE | DESCRIPTION                                                            | PACKAGE<br>REFERENCE       | PART NUMBER              | MANUFACTURER                   |

|--------------------------------|----------|-------|------------------------------------------------------------------------|----------------------------|--------------------------|--------------------------------|

| !PCB                           | 1        |       | Printed Circuit<br>Board                                               |                            | LP026                    | Any                            |

| C1, C3, C5, C7                 | 4        | 10uF  | CAP, CERM, 10 uF,<br>35 V, +/- 10%, X7R,<br>1206                       | 1206                       | GMK316AB7106KL           | Taiyo Yuden                    |

| C2, C6                         | 2        | 0.1uF | CAP, CERM, 0.1<br>uF, 50 V, +/- 10%,<br>X7R, AEC-Q200<br>Grade 1, 0603 | 0603                       | CGA3E2X7R1H104K0<br>80AA | TDK                            |

| C4, C8                         | 2        | 0.1uF | CAP, CERM, 0.1<br>uF, 16 V, +/- 10%,<br>X7R, 0603                      | 0603                       | C0603X104K4RACTU         | Kemet                          |

| FID1, FID2, FID3               | 3        |       | Fiducial mark. There is nothing to buy or mount.                       | N/A                        | N/A                      | N/A                            |

| H1, H2, H3, H4                 | 4        |       | Bumpon,<br>Hemisphere, 0.44 X<br>0.20, Clear                           | Transparent<br>Bumpon      | SJ-5303 (CLEAR)          | 3М                             |

| J1, J3, J5, J7                 | 4        |       | Header, 100mil,<br>3x1, Gold, TH                                       | 3x1 Header                 | TSW-103-07-G-S           | Samtec                         |

| J2, J4, J6, J8                 | 4        |       | Header, 100mil,<br>2x1, Gold, TH                                       | 2x1 Header                 | TSW-102-07-G-S           | Samtec                         |

| R1, R2                         | 2        | 0     | RES, 0, 5%, 0.063<br>W, 0402                                           | 0402                       | RC0402JR-070RL           | Yageo America                  |

| SH-J1, SH-J3, SH-<br>J5, SH-J7 | 4        | 1x2   | Shunt, 100mil,<br>Flash Gold, Black                                    | Closed Top<br>100mil Shunt | SPC02SYAN                | Sullins Connector<br>Solutions |

| U2                             | 1        |       | Ultra High-Precision<br>Voltage Reference                              | LCCC8                      | REF7025QFKH              | Texas Instruments              |

www.ti.com Overview

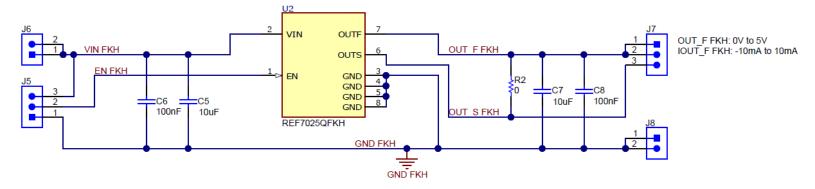

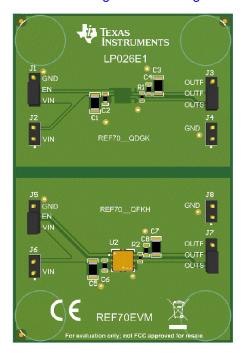

#### 1.4 REF70EVM Board

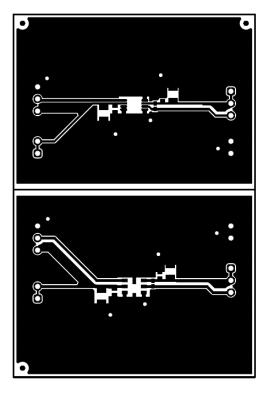

The PCB layout for the REF70EVM is illustrated in Figure 1-2 and Figure 1-3.

Figure 1-2. REF70EVM Board Top

Figure 1-3. REF70EVM Board Bottom

Quick Setup Guide www.ti.com

#### 2 Quick Setup Guide

This section describes the setup to quickly check the functionality of the REF70EVM.

#### 2.1 Electrostatic Discharge Warning

Many of the components on the REF70EVM are susceptible to damage by electrostatic discharge (ESD). Customers are advised to observe proper ESD handling precautions when unpacking and handling the EVM, including the use of a grounded wrist strap at an approved ESD workstation.

#### **CAUTION**

Failure to observe ESD handling procedures may result in damage to EVM components.

#### 2.2 Unpacking the EVM

After opening the REF70EVM package, ensure that the following is included:

1 pc. REF70EVM board using one REF7025QFKH

#### 2.3 Power Supply Setup and Functional Test

Normal operation:

A 5-V power supply capable of 50 mA of current is required. The REF70 consumes 6.5 mA of current during normal operationg and has a maximum 10 mA of output current for maintaining regulated voltage. During startup, the REF70 might consume  $I_{SC}$  momentarily to charge the output capacitors.

Connect the positive power supply lead to the "VIN" on J6. Connect the negative power supply lead to "GND" on J8.

Connect a voltmeter positive terminal to "OUTF" on J7. Connect the negative voltmeter terminal to "GND" on J8.

The output voltage of the REF7025QFKH will be 2.5V.

Shutdown mode:

The REF70 "EN" pin has an internal pull up which makes the REF70 be active when EN is floating. Use header J5 to connect "EN" to "GND" to put the device in shutdown mode.

#### 3 EVM Theory and Operation

The following schematic is representative of the REF70EVM.

Copyright @ 2020, Texas Instruments Incorporated

Figure 3-1. REF7025 Schematic

The REF70EVM is designed to allow users to evaluate the configuration in Figure 3-1. With the provided footprints, a user can change the passive components to better suit their application. As shown in Figure 1-2, the EVM is designed to allow users to evaluate the REF70 in FKH. This EVM also has the land pattern for the REF70 in DGK which allows users to test the device in their system with the provided pins.

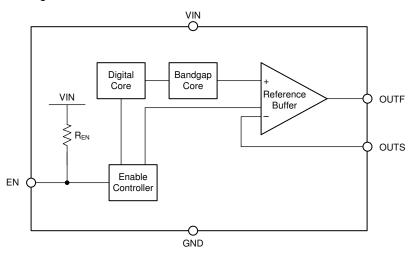

#### 3.1 V<sub>REF</sub> Output's OUTF and OUFS

The REF70 V<sub>REF</sub> is the output of the REF70 when the OUTF and OUTS are shorted together. OUTF and OUTS refer to the force and sense configuration of the REF70 reference buffer. The benefit of having force and sense connection is to reduce the IR loss from long trace wires at high currents. In the normal active configuration, the OUTF and OUTS are shorted together. In the REF70EVM this is done by the R1 and R2 which are 0 Ohm resistors. If R1 or R2 is removed, OUTF and OUTS must be connected in a loop by the headers J3/J7 or externally for proper operation. If the OUTF and OUTS are not connected together in a loop then the device will not operate the correct voltage.

Figure 3-2. REF70 Functional Block Diagram

## 3.2 Output Capacitor

The REF70 requires an output capacitor between 0.1 uF to 100uF for proper operation and stability. Larger capacitors are able to help with load transcient respones.

A large capacitor can also help with lowering the broadband/white noise. It is necessary to understand output capacitors when selecting the capacitor for the appliation.

## **4 Layout and Component Placement**

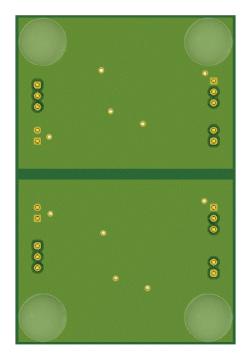

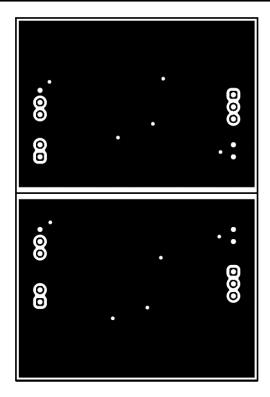

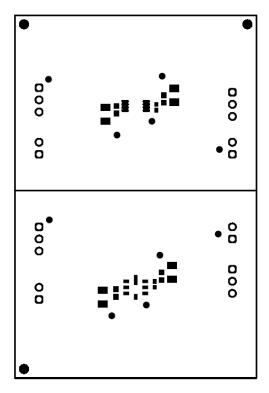

Figure 4 and Figure 5 show the top and bottom assemblies of the printed circuit board (PCB) to show the component placement on the EVM.

Figure 6 and Figure 7 show the top and bottom layouts, Figure 8 and Figure 9 show the top and bottom layers, and Figure 10 shows the top solder mask of the EVM.

Figure 4-1. Component Placement—Top Assembly

Figure 4-2. Component Placement—Bottom Assembly

Figure 4-3. Layout Top

Figure 4-4. Layout Bottom

Figure 4-5. Top Layer

Figure 4-6. Bottom Layer

Figure 4-7. Top Solder Mask

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated